Different Stages of IP Verification

The quality of semiconductor intellectual property (IP) is a major issue for design teams utilizing third-party sources for portions of their SoCs. Quality is even more critical for highly configurable types of IP because customers license it specifically to address the unique requirements of their systems and markets. The on-chip interconnect fabric is perhaps the most common example of highly configurable IP, and its quality is paramount to enable first-pass success for SoC creation.

Thorough verification is critical because the initial cost of configurability pales in comparison to the cost of slowing down a tapeout. Configurability enables customers to innovate in an infinite number of ways; however, its use also makes corner case verification extremely important.

To obtain sufficient quality, it is critical to use a configurable IP that has been proven in production SoC designs. If it has been implemented in large volume SoCs and has been verified at multiple design and production levels, then it has “proven” configurability. But even at this level, every customer makes certain risk tradeoffs for new IP – Do they want the most advanced features to address a new market? Do they want something proven and less risky? How to decide?

Trust but Verify: Introducing the 7 Stages

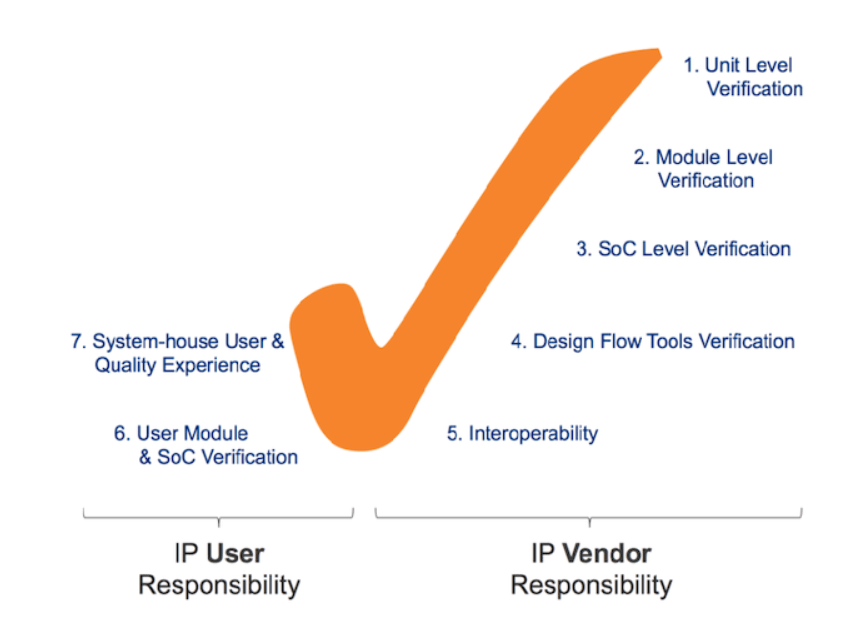

If your team wants to assume the least amount of risk and get to market promptly, then it has to evaluate an IP candidate on seven levels of verification. If a user wants to feel more comfortable with quality throughout the entire SoC life cycle, then the IP must pass all seven levels of verification described here:

- Unit-level – For units and elements that make up the configurable IP, this foundational level is critical to the process because bugs or issues found here will result in problems at subsequent levels.

- Module-level – This is generated in the actual user configuration that will be implemented in the SoC based on required performance parameters and topology. At this level, the configurable IP mates with the functionality of others in the design. It should be verified by the vendor first, and should be based on representative design examples and results should be made readily available to customers.

- SoC-level – The IP vendor should verify representative customer configurations using a number of sample SoC designs – ideally, provided by customers – to verify performance and quality. This includes release-to-release design performance drift verification.

- Design flow tool verification – This includes testing of any tools used to configure and generate the IP, whether the tool suite is controlled by the command-line, a graphical user interface (GUI), or both.

- Interoperability – The IP vendor needs to demonstrate testing results for transaction and communication protocols such as AMBA and customer proprietary protocols. Also, EDA tool and verification IP integrations with key partners should be demonstrated.

- Customer module and SoC verification – Occurs during the design, tapeout, bring up and debug phases. The customer should be able to implement, integrate and verify the customer-configured IP at the same or higher confidence as if it were hand-coded by an internal team.

- Customer, system-level user and quality experience – Includes system house and end-customer system lifecycle testing.

The most important parts of the verification sequence are the last two customer phases. Here, it is critical that an IP company possess the people, culture, processes, and execution in its internal verification program to not only ensure that the IP vendor delivers quality IP, but also enables customers to easily verify their own custom configurations of the IP. This is a long-term process and requires a relationship of trust between the IP vendor and user because although users can perform all varieties of testing and verification until they successfully deploy the IP insufficient volume they won’t know what problems will be encountered. Anticipation and analysis do not equal first-hand knowledge. This is why vendors that have to design wins for a narrow set of target applications often encounter deployment problems outside of their originally targeted market space.

Quality Takes Time

Because the initial price of the configurability is relatively small compared to the potential impact on SoC delivery, it is essential to deliver proof in processes, procedures, time, and experience to ensure customer confidence. Additionally, the technical benefits of anything new must far outweigh the potential risks to function, quality, and delivery schedule. These are the main reasons why it takes about 10 years to build a strong IP company: The provider not only has to build the product but also must get it designed into a sufficiently broad set of applications. Then the customer must successfully deliver the SoC and have system houses incorporate the chips. Finally, the customer has to deliver sufficient volumes to prove that the quality has a positive impact on its system-house business. Only then can the value of quality be correctly quantified.

In this process, IP vendors have to keep up with major technology changes and specific customer requests while maintaining strong support and impeccable quality. This is not easy to accomplish. As a result, successful companies like ARM, Synopsys, Imagination, Tensilica, and Arteris were not built quickly. That’s because it takes time for the product to achieve the seven levels of verification and production volume success.

Commercial vs. Internal Development

Achieving these verification levels requires the configurable IP vendor to experience a broad range of SoC designs implemented into a variety of systems, which ideally results in a higher quality product than is possible to develop internally. Quality at this level is difficult for internal interconnect groups in all but the largest semiconductor companies to attain because internal teams see a relatively small number of designs and a relatively narrow variety of design methodologies.

A rule of thumb: The greater diversity and number of successful system design-ins, the greater the quality and ultimately the value of configurability.

Interoperability and Ecosystems

A configurable IP is just one of the hundreds of components and subsystems that make up an entire SoC. Therefore, the ecosystem around it is quite important. Interfaces to others must be tested and interoperability must be assured. In particular, ARM’s AMBA standards have emerged as being the most widely adopted, therefore it is very important for vendors to monitor and implement the stream of ARM standard developments in order to assure trouble-free customer integration.

Customers also use a variety of EDA tools and methodologies that have to be tested with configurable IP to assure smooth interoperability. Customers want to focus on design and don’t need to be sidetracked with interoperability problems. Ecosystem testing and verification are in the best interest of all involved as seamless integration accelerates the use of all IP involved. The vendor needs to complete this early in the process before interoperability issues start hitting development schedules.

Quality Makes Commercial IP Possible

Of course, verification and quality are not the only considerations for adoption. New technologies and standards emerge all the time and configurability has to support this continuous evolution. Innovations that improve the quality of results and productivity must also translate into reduced SoC costs. Therefore, the selection of IP involves a trade-off between technology benefits, cost reductions, and quality risk.

If the technology benefit is high enough, the quality risk will be worth taking. For example, low-power processor cores, configurable processors, high-performance GPUs, and network-on-chip interconnects were once unproven technologies developed and marketed by small companies. Today, they are proven in some of the most complex SoCs ever made, leading to a virtuous cycle of greater customer comfort and adoption, superior quality, and higher technological investment and innovation. The secret is that all these technologies evolved through solid quality programs and global support organizations.

A quality electronic system, made up of quality SoCs, needs to be made of fully verified components. It is vital for chip designers then to scrutinize any candidate IP with the seven levels of IP verification to warrant consideration.

Source: https://www.edn.com/the-7-levels-of-ip-verification/