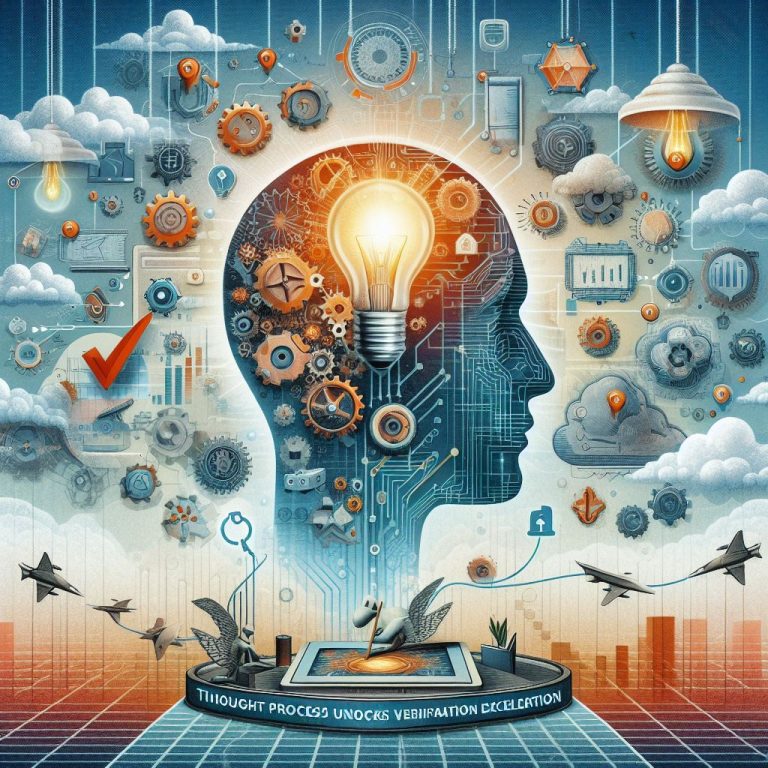

From RTL to Reality: Unlocking the Secrets of Hardik’s Design Verification Odyssey

In the ever-evolving world of chip design, where circuits dance with logic and transistors tango with electrons, stands a breed of unsung heroes: the ASIC verification engineers. These digital detectives, armed with their arsenal of tests, hunt down bugs with the zeal of Indiana Jones and the precision of a Swiss watchmaker. Today, we delve…