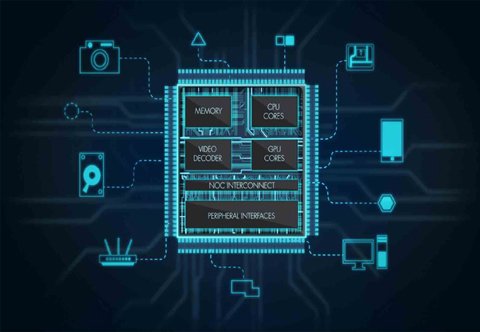

Key Areas to consider during SOC Verification

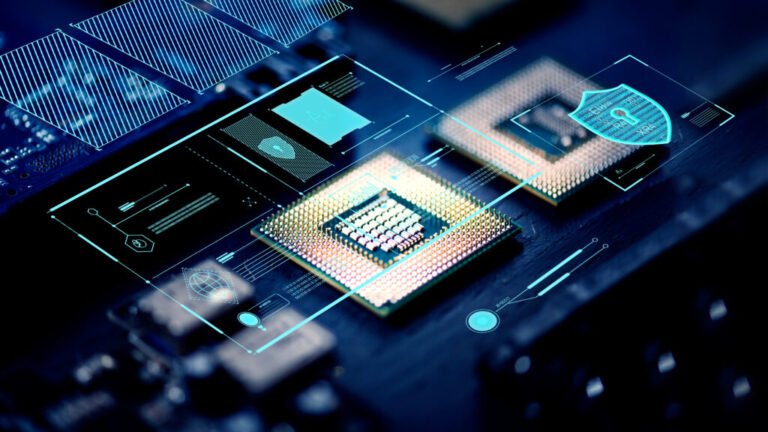

Over the years, design complexity and size have stubbornly obeyed the growth curve predicted by Intel co-founder Gordon Moore. Moore stated that the number of transistors on integrated circuits doubles approximately every two years. The chip makers want to pack as many functions as possible in their SoCs and provide as many feature additions to…